英特尔领先全球,独占鳌头:18A工艺力压台积电2nm技术,提早一年引领科技革命!

近日,Intel 在官网上正式介绍了其最先进的 Intel 18A 制程工艺,并表示该技术已“准备就绪”。据外界预测,Intel 18A 将于 2025 年年中开始量产,首发产品将是酷睿 Ultra 300 系列“Panther Lake”处理器,预计在今年下半年上市。 Intel 这次的技术突破无疑为其在半导体领域中的竞争增添了新的筹码。随着 Intel 18A 的到来,我们有望看到更高效的处理器以及更低功耗的产品。尽管目前市场上已有多种先进制程工艺的竞争者,但 Intel 18A 的推出仍然令人期待,尤其是在性能和能效方面可能带来的显著提升。让我们拭目以待,看看 Intel 能否凭借这一新技术重振其在芯片制造领域的领导地位。

能效提升15%,密度提升30%

根据Intel官网的介绍资料显示,与Intel3工艺节点相比,Intel18A的每瓦性能提升15%,晶体管密度增加30%。Intel称其为北美最早能够量产的2nm以下先进工艺节点,可为客户提供更加稳定的供应选择。

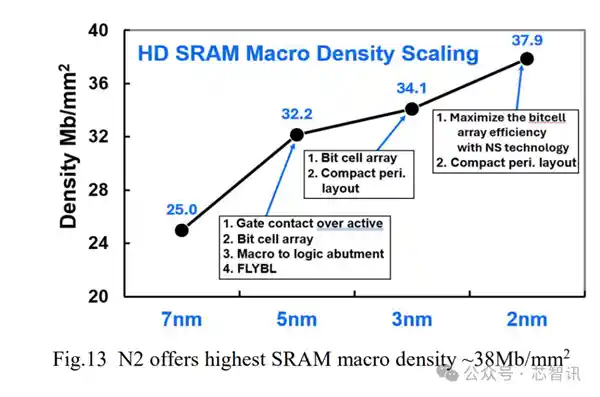

此外,根据已曝光的资料显示,Intel 18A的SRAM密度达到了0.021μm²的高密度SRAM位单元尺寸(实现了大约31.8Mb/mm²的SRAM密度),与Intel 4的0.024μm²的高密度SRAM位单元尺寸相比,这是一项显著的进步。

根据研究机构TechInsights的测算,Intel 18A的性能值为2.53,而台积电N2的性能值为2.27,三星SF2的性能值则为2.19。从这些数据可以看出,Intel在先进制程工艺上的表现似乎更胜一筹。尽管台积电和三星在半导体制造领域一直占据主导地位,但Intel的新工艺似乎正在缩小这一差距。这不仅反映了Intel在研发上的巨大投入,也预示着未来半导体市场竞争可能会更加激烈。

也就是说,英特尔的Intel18A在2nm级工艺中依然保持着领先优势,台积电的N2紧随其后位列第二,而三星的SF2则排在了第三位。这种技术上的竞争无疑为芯片制造业注入了新的活力。各大制造商之间的激烈角逐不仅推动了技术的进步,也使得消费者能够更快地享受到更高效能的产品。此外,这种竞争态势还促使各公司在研发上加大投入,以期在未来的技术迭代中占据更有利的位置。

RibbonFET晶体管

Intel 18A采用了RibbonFET 环栅 (GAA) 晶体管技术,可实现电流的精确控制。RibbonFET 可进一步缩小芯片组件体积,同时减少漏电,这对于日益密集的芯片而言是一个关键问题。

RibbonFET提升了每瓦特的性能、最低工作电压(Vmin)以及静电特性,因此带来了明显的性能优势。

RibbonFET还通过多样的带宽和多种阈值电压(Vt)类型提供了高度的可配置性。HDMIM电容器能有效减少电感损耗,提升芯片的稳定运行性能。

此功能对于生成式 AI 等需要突然且高强度计算能力的现代工作负载至关重要。

Intel去年底公布的信息显示,为了将RibbonFET GAA晶体管的微缩推向更高水平,Intel代工部门展示了栅极长度为6纳米的硅基RibbonFET CMOS晶体管,在大幅缩短栅极长度和减少沟道厚度的同时,在对短沟道效应的抑制和性能上达到了业界领先水平。Intel称,这一进展为摩尔定律的关键基石之一——栅极长度的持续缩短——铺平了道路。

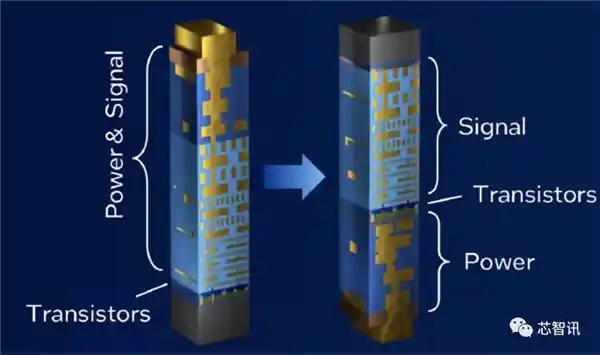

PowerVia 背面供电技术

随着晶体管密度的增加,混合信号和电源布线会造成拥塞,从而降低性能。

Intel代工厂推出的创新技术PowerVia,通过将较为宽距的金属层和焊盘移至芯片背面,并在每一个标准单元内部集成纳米级硅通孔(nano-TSV),从而实现了更为高效的电力分配方案。

Intel 18A将率先引入业界首创的PowerVia背面供电技术,这不仅能够提升5%到10%的密度和单元利用率,还能显著降低电阻,从而减少供电下降的问题。这使得整体的性能提高了大约4%,同时与正面供电设计相比,IR下降也得到了大幅缓解。 这一技术突破表明,Intel在半导体制造工艺上的创新步伐正在加快。特别是在当前竞争激烈的市场环境中,这种技术进步无疑会为Intel带来显著的竞争优势。随着对更高性能和更小尺寸芯片需求的不断增加,Intel的这一举措有望帮助其巩固行业领导地位,并可能重新定义高端芯片市场的格局。

相比之下,三星计划于2026年实现SF2P工艺的量产,这标志着他们将在该节点上首次采用背面供电技术。而台积电方面,预计要到2026年甚至更晚的2027年,在其A16工艺上才能看到背面供电技术的应用。 这一进展不仅反映了两家公司在半导体制造技术上的竞争态势,也展示了各自在技术创新方面的不同步调。三星在这一关键技术上的提前布局,可能会为其赢得更多高端芯片市场的份额。然而,这也意味着台积电需要加快步伐,以确保在未来的市场竞争中不落后于人。两者之间的技术竞赛无疑将推动整个行业向前发展,消费者最终也将从中受益。

不过,预计台积电的A16背面供电设计将采用直接背面连接方式,有望实现比英特尔和三星的方案更低的轨高。

生态系统

该工艺还全面支持行业标准 EDA 工具和参考流程,实现从其他技术节点的平稳过渡。借助 EDA 合作伙伴提供的参考流程,我们的客户可以先于其他背面电源解决方案开始使用 PowerVia 进行设计。

英特尔指出,目前由超过35个行业领先的生态系统合作伙伴组成的强大团队正在发挥作用,这些合作伙伴涵盖了电子设计自动化(EDA)、知识产权(IP)、设计服务、云计算服务以及航空航天和国防等多个领域。这不仅有助于确保广泛的客户支持,还能进一步简化复杂的设计流程。 这一举措展示了英特尔在构建强大生态系统的决心,并且通过与众多领域的顶尖企业合作,英特尔能够在技术开发和应用方面获得更多的资源和支持。这种开放的合作模式不仅能够加速技术创新,还能够帮助更多企业克服技术障碍,推动整个行业的进步和发展。

最快2025年上半年量产

早在去年9月,Intel就在俄勒冈州波特兰市举行的 Enterprise Tech Tour 活动中,首次展示了基于Intel 18A制程的代号为Clearwater Forest的Xeon芯片。

随后在10月,Intel宣布已向联想等合作伙伴提供了采用Intel18A制程的PantherLake CPU样品。

目前预计Intel的18A制程技术将于2025年年中进入量产,最快可能在上半年就开始。这一技术将首先应用于酷睿Ultra 3系列“Panther Lake”处理器上,该处理器计划在今年下半年上市。从目前的情况来看,Intel似乎正按计划推进其先进制程技术的发展,并有望为市场带来性能更为强大的处理器产品。这不仅标志着Intel在半导体技术领域的持续进步,也可能对整个行业产生积极的影响。随着更多采用18A制程技术的产品陆续推出,我们期待看到这些新技术如何进一步推动计算能力的边界。

相比之下,台积电的 N2 计划于 2025 年底进行大批量生产,该节点生产的第一批产品最早要到 2026 年年中才能上市,相关产品预计将于 2026 年秋季上市。

这表明Intel的18A制程技术有望比台积电的N2制程提前大约一年完成开发。这一进展不仅突显了英特尔在半导体制造领域的强劲势头,还可能重新定义芯片行业的竞争格局。随着技术节点的不断缩小,每家公司在先进制程上的突破都显得尤为关键。英特尔若能按计划推进,将为其带来显著的技术优势,并可能吸引更多寻求最尖端技术的客户。不过,值得注意的是,尽管时间表看起来很有利,但在如此复杂的领域,实际量产和应用过程中仍存在诸多不确定因素。

High NA EUV有望继续扩大优势

在Intel18A领先台积电N2约一年的时间内,Intel正在利用ASML最新的HighNA EUV光刻机来进一步巩固其技术优势,因为这种设备是实现1nm级先进制程所必需的制造工具。

根据此前Intel透露的消息,Intel计划在Intel 18A之后的Intel 14A节点上采用High-NA EUV光刻机。相较于Intel 18A工艺,Intel 14A工艺的晶体管密度预计将提升20%。

目前,Intel在HighNA EUV技术领域同样占据领先地位。之前,Intel已购入两台价值3.5亿美元的ASML Twinscan EXE5000系列High NA EUV光刻机,并于去年完成安装和调试工作。截至目前,Intel是唯一一家积累了丰富使用此类设备经验的半导体制造商。

相比之下,之前台积电负责业务开发的资深副总裁张晓强表示,尽管他对HighNAEUV的技术能力印象深刻,但设备成本过于高昂。

台积电凭借现有的极紫外光(EUV)技术,预计可以支撑其芯片生产至2026年底。到了那时,台积电的A16制程技术也将采用当前标准型的EUV光刻设备进行大规模生产。 这样的进展表明,台积电在尖端制造工艺上依然保持着行业领先地位,并且通过持续的技术积累和研发投入,确保了其在未来几年内仍能保持竞争优势。这不仅有助于巩固其在全球半导体供应链中的关键角色,也为其客户提供了稳定可靠的生产支持,特别是在当前全球芯片短缺的背景下,这种稳定性显得尤为重要。

台积电正在考虑使用HighNA EUV光刻机来生产A10制程芯片。不过,在此之前,有消息称台积电已开始着手提前引进HighNA EUV技术以积累相关经验。

此前,Intel公司硅光子部门首席项目经理JosephBonetti在LinkedIn平台上发布文章指出,与竞争对手相比,Intel在High-NA EUV技术方面至少领先一年。

免责声明:本站所有文章来源于网络或投稿,如果任何问题,请联系648751016@qq.com

页面执行时间0.009719秒